iPhone 5 Launch: Will Apple Use ‘Macroscalar’ Architecture in Upcoming Smartphone for Better Processor Performance?

Rumors are rife that iPhone 5 is coming soon and Apple's next generation smartphone will have some stunning features which will outshine those of all its competitors.

The latest rumor regarding iPhone 5 suggests that the phone is going to get the Macroscalar processor architecture, which will improve the speed and functionality of its processor.

Apple is expected to launch the A6 processor for iPhone 5 and iPad 3. The A6 processor will boost the performance of upcoming iPad and iPhone, while consuming less power.

According to AppleInsider, Jeffry Gonion, who has worked as a platform architect at Apple since 2003, is the inventor of the concept of the Macroscalar processor architecture. Gonion developed the concept of the macroscalar processor architecture as a technique for making optimized, efficient use of a processor's execution pipelines by preparing and ordering instructions so they can be executed in parallel as much as possible.

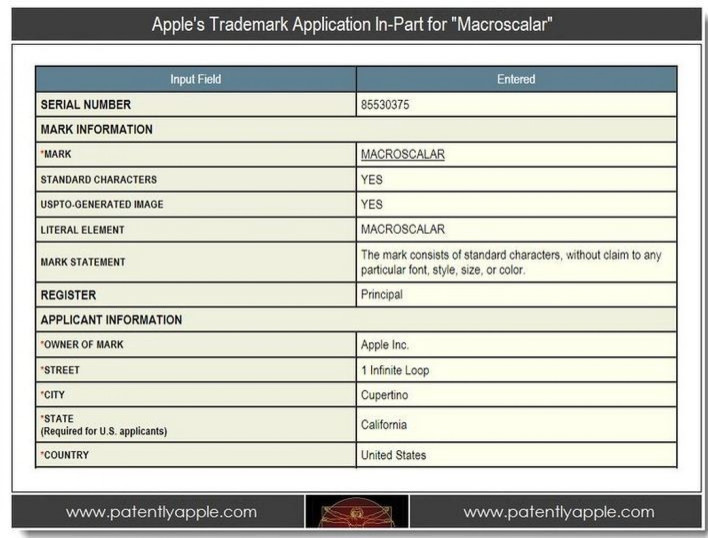

Early last week, a surprising trademark application from Apple for the word Macroscalar was published by the U.S. Patent & Trademark Office.

Till now, Apple has always quietly registered trademarks in countries like Trinidad & Tobago and only after announcing the new products and features, the company applied for the marks in the United States and other major markets.

While an application for Macroscalar was filed in Trinidad & Tobago last August, the new U.S. application and a similar one in Hong Kong are fueling the speculation that Apple will introduce a new and better processor technology this time.

Experts believe Apple Inc., which has always filed for trademarks focusing less on underlying technology and more on consumer-facing features, will use the Macroscalar technology this time to get a better marketing benefit for its upcoming iPhone 5 and iPad 3.

In July 2010, ZDNet carried an article and explained Apple's macroscalar architecture. The macroscalar processor addresses this problem in a new way: at compile-time it generates contingent secondary instructions so when a data-dependent loop completes the next set of instructions are ready to execute. In effect, it loads another pipeline for, say, completing a loop, so the pipeline remains full whether the loop continues or completes. It can also load a set of sequential instructions that run within or between loops, speeding execution as well, the article stated.

© Copyright IBTimes 2024. All rights reserved.